|

KX-CPDS4S+

收藏

随着电子技术的发展,核心技术已经愈来愈集中在集成电路芯片和软件之中,其中CPU和OS设计技术是最为核心的技术。特别是高性能计算机技术一直是衡量国家实力的一个重要标志。美国的高校本科计算机专业中都无一不是安排了CPU硬件设计方面的课程和实验内容。例如麻省理工学院的一门相关课程就是《计算机系统设计》。学生在实验课中,须自主完成ALU、单指令周期CPU(single cycle CPU)、多指令周期CPU,乃至实现流水线32位MIPS CPU和Cache的设计;Stanford大学计算机系的本科生也有相似的课程和实验,即《计算机组成与设计》课。实验要求学生以各自独立的形式,用硬件描述语言自主实现CPU、VGA显示控制模块等接口,最后实现于FPGA中,并完成软硬件调试。此外,如University of California和Berkeley和Brigham Young University等学校在基于FPGA的超级计算机研制方面也有大量成果。 然而我国高校计算机专业对等课程的教学情况总体而言不容乐观。尽管也通常包含了《计算机组成原理》的课程,但调研表明,多数学校仅将此课程定位在计算机模型认知的层面上;而在实验与实践方面,此课程的实验则主要是完成由分离元件构成的简单模型CPU的验证性实验,根本谈不上与实际工程相联系的设计,更没有国外高校类同的自主创新型CPU设计任务,以及与现代计算机系统硬件设计工程相吻合的教学与实践内容。这导致了国内大多数计算机专业人才知识结构一直存在的“偏软怕硬”的缺陷。 针对这一情况, 科学出版社就于2007年就推出了《现代计算机组成原理》一书,潘松等教授编著。该教材后被评为国家级精品教材(上图。在当年国内高校所有专业教材中,评选出的218种教材中,该书是唯一涉及计算机组成原理的教材)。《现代计算机组成原理》第二版(上图。2013年)提供了基于现代计算机设计技术的关于CPU和计算机系统硬件设计理论和设计技术方面较完整和丰富的内容。其中有基于单片FPGA硬件平台的微程序控制模式的8位CISC模型计算机原理和设计技术;16位实用CISC CPU的基本原理、设计技术和创新实践指导;基于流水线技术的RISC CPU设计技术;基于32位OpenRISC1200处理器系统的SOC构建和应用设计以及基于经典处理器的8051CPU核与8088/8086 CPU核构建SOC(System Of a Chip)系统的基本理论和设计技术。对应每一章,还提供了有针对性的实验与实践项目,甚至包括激发学习者创新意识和培养创新能力的CPU创新设计竞赛项目。 近些年中,认可并实践此教材基本教学理念和教学实验内容的高校不断增加,其中许多高校的计算机专业选择此书作为教材或选择教材中提到的FPGA实验系统来完成对应的硬件实验;这些学校有西安交大、西北大学、中国人民大学、吉首大学、哈工大、北航、中国民航大学和南邮、大连理工等三十余所高校。最难得的是,最早加入这一教改行列的学校竟然是一所外语学校,即广州外语学院。该校有关老师对于外语专业学生兼修计算机软件技术和基于FPGA的计算机硬件设计技术在拓宽就业口径,提高就业率方面所表现出的优势有很高的评价。 利用QuartusII软件的强大功能:

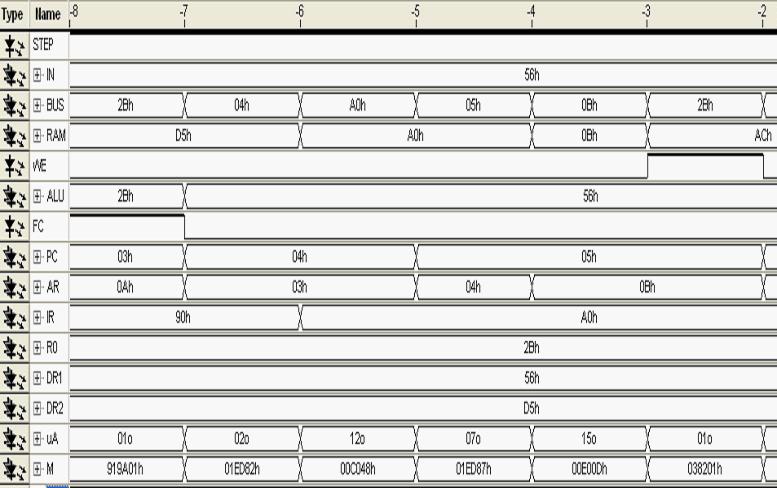

利用QuartusII的In-System Sources and Probes实时测试载入FPGA中的8位模型机执行指令的波形其中的M、uA、RAM、BUS、WE分别是微指令、微地址、存储器、总线数据、RAM写允许等信号

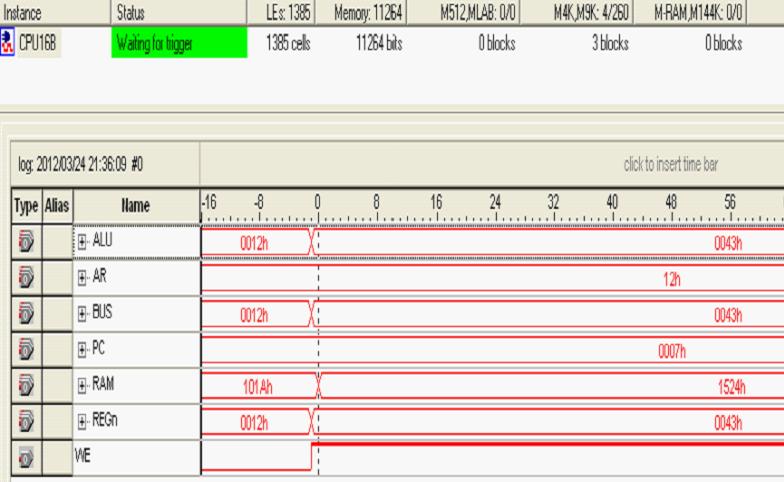

利用嵌入式逻辑分析仪对载入FPGA中的16位CPU的运行情况进行实时测试的波形和数据

对于加法指令和存数指令在16位CPU中的执行情况的仿真波形片段 型号:KX-CPD4S+(具体参数可咨询客服) 第一部分:核心板 1、CycloneIV型FPGA EP4CE55F484脚 。含55856个可编程逻辑宏单元,2396160个SRAM存储单元、4个锁相环。 2、16M FPGA专用配置存储器EPCS16。 4、32 MB SDRAM.支持8位和16位总线。 5、64 MB FLASH 串行存储器。 6、TF卡接口 7、5个单脉冲式开关 8、2组十芯可扩展IO口 9、扬声器。 10、2组20MHz有源晶体振荡器。用于驱动FPGA中的4个锁相环。 11、VGA接口及其适配电路。 12、PS/2 鼠标/键盘接口。 13、点阵和字符液晶接口。 14、两组共80芯扩展接口。 15、语音输入、输出处理接口 第二部分:主系统 1、KX_USB-Blaster2型双功能编程器:(1)USB-Blaster编程下载功能(支持AS、PS、JTAG模式):1、对FPGA/CPLD进行配置或编程;2、对配置器件EPCSx编程;3、访问和编辑FPGA内部RAM;4、调试Nios2,完成SOPC设计;5、支持SignalTapII 嵌入式逻辑分析仪。 (2)USB到UART串行通信转换:1、通过USB与FPGA串行通信,实现PC与FPGA的串行通信,且无需RS232电平转换;2、通过USB与单片机的串行通信,实现PC与通用单片机的UART串行通信;3、通过USB对STC等系列单片机进行直接编程开发,无需电平转换。 2、多功能重配置型高效率实验控制电路。主系统板上含有Multi-task Reconfiguration(多功能重配置结构)控制电路。该电路结构能仅通过一个键的控制,实现纯电子方式切换,选择十余种面向不同实验需要的针对FPGA目标芯片的硬件电路连接结构。 3、FPGA中运行多种经典实用处理器IP核。系统允许在核心板的大规模FPGA中运行多种经典实用软硬处理器IP核,包括:(1)基于微指令的8位模型处理器、(2)基于状态机指令控制结构的16位实用处理器、(3)基于精简指令流水线结构的16位处理器(4)8051软核处理器(基于商业级全兼容MCS-51单片机IP核。利用此核,实验者可以实现传统单片机实验系统无法达到的SOC(片上系统)设计。即将单片CPU、RAM、ROM以及其它各类接口电路模块设计在同一片FPGA中、(5)32位软核NiosII Gen2嵌入式系统处理器。 4、5功能智能逻辑笔:可显示高电平、低电平、中电平、高阻态、脉冲信号。注意有“高阻态”测试功能。 5、独立的标准时钟频率20个。20M~0.5HZ,从低到高20组时钟可供选择(对于初学者多频可选很重要)。 6、电源有自动保护的+5V,+12V、-12V、、+3.3V、2.5V+、1.2V。 7、8个LED放光二级管,8个拨码开关,扬声器。 8、DDS信号输出口及幅度、偏移调谐。 9、6个标准可扩展IO十芯座,1个十四芯座;4组可扩展模块座,1个可扩展DDS模块座、一个可扩展7寸彩屏液晶座; 10、CPLD3032 11、含扫描的智能译码电路模块,12个按键、其中按键可切换成脉冲式、高低电平式、输出4位二进制式电路模式,8数码可切换成直通非译 码动态扫描式、智能BCD译码、16进制译码;16个发光二极管; 第三部分:扩展模块 模块1:4X4+8个单脉冲综合键盘模块 模块2:字符型液晶显示屏 模块3、480*800TFT液晶显示模块(显示数据运行情况) 模块4、32位输出显示HEX模块 模块5、32位输入显示HEX模块 第四部分:实验内容 组成原理实验(基于FPGA单片完成) ●算术ALU运算器、可完成8位加法,减法等及逻辑运算功能; ●带进位ALU运算器实验; ●基于FPGA的LPM_ROM; ●单双口LPM_RAM; ●LPM_FIFO定制读写实验; ●微控制器时序电路; ●程序计数器PC与地址寄存器AR实验; ●地址寄存器实验; ●微控制器设计; ●微指令控制器实验; ●微地址寄存器电路实验; ●微地址译码器实验; ●总线控制; ●移位运算器实验; ●连续节拍发生器实验; ●单步节拍发生器实验; ●单步/连续节拍发生器实验; ●锁相环应用; ●嵌入式逻辑分析仪应用等等; ●8位模型机的设计与实现; ●基于状态机的完整16位CPU设计; ★8051核单片机实验: ●8051核基本用法 ●8051_74164_65串进出 ●8051_RAM读写 ●8051_4通道PWM发生器 ●8051_等精度频率计 ●8051_128*64点阵液晶字符 第七部分、提供的软件资源 1、资质证书 (1)杭州市高校技术企业 (2)多任务重配置技术专利 (3)16CPU设计专利 (4)ATERA颁发的“终身成就奖” (5)科学出版社颁发的“优秀作者奖” 1、基本软件:1)Quartus II 9.0/13.1;2)8051单片机IP核;3)Nios II软件; 2、实验配套资源:提供相关的实验指导书,组成原理实验指导书、提供相应PPT课件、PDF教学文档等。提供扩展板原理图。实验指导书及其电子版。 3、配套教程 潘松 教材 (1)科学出版社《EDA技术实用教程》Verilog/VHDL《现代计算机组成原理》 (2)清华大学出版社出版的《EDA技术与VHDL/VerilongHDL》(可自行订购)。 (3)清华大学出版社出版的《现代计算机组成原理》(可自行订购)。 |