|

KX-CDS5S可扩展DE1-SOC

收藏

产品概述: KX-CDS系列EDA/SOPC/组成原理系统是由三个既独立又相关的部分组成的,它们是:含有FPGA和不同接口电路的核心插板;适用于自主创新实验与开发的模块化自由插件电路系统;以及适合于初学者快速高效入门学习的多功能重配置型实验控制系统。这三部分可以综合应用,方便而高效的完成不同类型不同层次和不同学科分支领域(如FPGA实用电子设计、计算机组成原理实验、DSP设计与实验、计算机接口、SOC片上系统、自动化控制等等)的EDA实验与开发。这三部分由集中体现了KX-CDS系统显著特征,即: 第一部分、模块化自主创新实验设计。 第二部分、多功能重配置型高效实验控制。 第三部分、适用于接插含不同规模FPGA的核心板的灵活结构。 可完成以下学科实验具体课程包括(根据不同的核心板),: (1)面向现代数字系统的数字电路基础课; (2)EDA技术(包括硬件语言); (3)SOPC/SOC技术; (4)现代计算机组成原理; (5)基于片上系统的单片机技术; (6)现代DSP技术(基于FPGA中的各类IP核构建的DSP系统); 第一部分:模块化自主创新实验设计结构 通常,诸如EDA、单片机、DSP、SOPC等传统实验平台多数是整体结构型的,虽也可完成多种类型实验,但由于整体结构不可变动,实验项目和类型是预先设定和固定的,很难有自主发挥和技术领域拓展的余地,学生的创新思想与创新设计如果与实验系统的结构不吻合,便无法在此平台上获得验证;同样教师若有新的创新型实验项目,也无法即刻融入固定结构的实验系统供学生实验和发挥。因此,此类平台不具备可持续拓展的潜力,也没有自我更新和随需要升级的能力。 因此,考虑到本教材给出的设计类示例和实验数量大、种类广,且涉及的技术门类较多,如包括一般数字系统设计、EDA技术、SOPC、计算机接口、计算机组成与设计、各类IP的应用、基于MCU核与8088/8086 IBM系统核的SOC片上系统设计、数字通信模块的设计、机电控制等,故选择KX_CDS系列模块自由组合型创新设计综合实验开发系统作为本教材实验设计硬件实现平台(位于主系统的右侧,上面可根据需要换插其它模块),能较好地适应实验类型多和技术领域跨度宽的实际要求。 这种模块化实验开发系统的主要优势可归纳为: ▲由于系统的各实验功能模块可自由组合、增减,故不仅可实现的实验项目多,类型广,更重要的是很容易实现形式多样的创新设计; ▲由于各类实验模块功能集中,结构经典,接口灵活,对于任何一项具体实验设计都能给学生独立系统设计的体验,甚至可以脱离系统平台; ▲面对不同的专业特点,不同的实践要求和不同的教学对象,教师,甚至学生自己可以动手为此平台开发增加新的实验和创新设计模块; ▲由于系统上的各接口,以及插件模块的接口都是统一标准的,可提供所有接口电路,因此此系统可以通过增加相应的模块而随时升级。 第二部分 多功能重配置型高效实验控制系统(此功能经过近20年的用户实践证明,非常适合集成芯片实验教学系统使用)以上的模块化自主创新实验设计结构主要是面向EDA技术学习已有较好实践基础的学生,更有利于深入学习和创新实践。而对于初学者,如果仅仅需要验证或学习一些并不复杂的设计项目,则希望实验控制尽可能简单,尽可能少的动用系统资源,甚至尽可能少的动用各种陌生的开关插件,一句话,尽快高效简洁的见到实验结果。此外,传统的手工插线方式虽然灵活,由于插线长、多、乱,会严重影响系统速度、系统可靠性和电磁兼容性能,不适合以高速见长的FPGA/SOPC等电子系统的实验与设计。 为此,KX-CDS系列主系统板上配置了Multi-task Reconfiguration(多功能重配置结构)控制电路(位于主系统的左下方)。该电路结构能仅通过一个键的控制,实现纯电子方式切换,选择十余种面向不同实验需要的针对FPGA目标芯片的硬件电路连接结构,并且毫不影响系统工作速度,大大提高了实验系统的连线灵活性,免除了传统情况下由于大量实验连接线导致的低效率,电路低可靠性,以及实验目标系统的低速性。利用这个系统,初学者能很快上手,无需接插任何模块和插线,就能在此实验系统上简洁而快速地完成大量不同类型的实验,迅速熟悉FPGA的硬件开发技术,为利用以上介绍的模块化自主创新实验结构,完成更高层次的创新实验奠定基础。 其实所采用的Multi-task Reconfiguration技术已被广泛应用,如虚拟仪器、通用编程器等。使系统的灵活性和高速特性两方面都得到了充分的满足。 第三部分 不同功能类型的FPGA核心板对于不同的实验实践者或学习者,以及不同的实验需要与开发目的,将对核心板会有不同的要求,这包括不同系列、不同封装,不同逻辑规模的FPGA,以及不同的接口功能模块(例如不同的ADC、DAC、网络接口、显示方式、各类通信模块、RAM/ROM、时钟源,不同频率的有源晶体振荡器,等等)。 为了方便这些需求,KX_CDS系统安排了这样一个通用电路结构(位于主系统的左上方),在这个电路结构区域,实验者可以预先插上需要的核心板。这些核心板根据需要可以有多种选择,这些板所包括康芯的各类核心板FPGA有:Cyclone4型的EP4C6/10E144/4C55F484,Cyclone3型的EP3C40E244,Cyclone10型的4\10CE055F23CB。等。还包括有晶公司的DE0型板(FPGA是Cyclone 3型的EP3C16F484)、DE0-CV型板(FPGA是Cyclone 5型的5CEBA4F23C7N)、DE1-SOC型板(FPGA是Cyclone 5型的FPGA 5CSEMA5F31C6N)。

配套教材主要有:

1.科学出版社的《EDA技术实用教程-Verilog版》第6版; 2.科学出版社的《EDA技术实用教程-VHDL版》第6版; 3.清华大学出版社的《EDA技术与VHDL》第5版; 4.《EDA技术与Verilog HDL》第3版,其中详细介绍了硬件描述语言,QuartusII、DSP-Builder应用开发等; 5.清华大学出版社的《单片机原理与应用技术》。介绍了FPGA与单片机接口技术及8051片上系统SOC应用; 6.科学出版社的《数字电子技术基础》。基于全新的数字电子技术教学理念; 7.科学出版社的《现代计算机组成原理——结构,原理,设计与SOC实现》; 8.清华大学出版社的《微机原理与接口技术——基本原理,实用技术和基于FPGA的SOC技术》; 9.清华大学出版社的《SOPC技术实用教程》,等。 一般集成芯片作为实验系统面临三大尴尬! 一、主芯片更新换代怎么办; 二、有限的IO口怎能满足数个实验要求; 三、层出不穷的新技术接口出现怎么解决; 如果您手头有DE1-SOC系列板,可为您加装扩展系统,使您教学系统更加完善。也可提供DE系列+主系统+扩展板完整系统,让您的资源更能得到充分利用!让您的教学实验更加丰富! 参数配置:(具体参数可联系客服) 第一部分:待扩展FPGA核心板 DE1-SOC,详细参数可查询资料。 第二部分:扩展主系统 1、KX_USB-Blaster2型双功能编程器:(1)USB-Blaster编程下载功能(支持AS、PS、JTAG模式):1、对FPGA/CPLD进行配置或编程;2、对配置器件EPCSx编程;3、访问和编辑FPGA内部RAM;4、调试Nios2,完成SOPC设计;5、支持SignalTapII 嵌入式逻辑分析仪。 (2)USB到UART串行通信转换:1、通过USB与FPGA串行通信,实现PC与FPGA的串行通信,且无需RS232电平转换;2、通过USB与单片机的串行通信,实现PC与通用单片机的UART串行通信;3、通过USB对STC等系列单片机进行直接编程开发,无需电平转换。 2、多功能重配置型高效率实验控制电路。主系统板上含有Multi-task Reconfiguration(多功能重配置结构)控制电路。该电路结构能仅通过一个键的控制,实现纯电子方式切换,选择十余种面向不同实验需要的针对FPGA目标芯片的硬件电路连接结构。 3、FPGA中运行多种经典实用处理器IP核。系统允许在核心板的大规模FPGA中运行多种经典实用软硬处理器IP核,包括:(1)基于微指令的8位模型处理器、(2)基于状态机指令控制结构的16位实用处理器、(3)基于精简指令流水线结构的16位处理器(4)8051软核处理器(基于商业级全兼容MCS-51单片机IP核。利用此核,实验者可以实现传统单片机实验系统无法达到的SOC(片上系统)设计。即将单片CPU、RAM、ROM以及其它各类接口电路模块设计在同一片FPGA中、(5)32位软核NiosII Gen2嵌入式系统处理器。 4、5功能智能逻辑笔:可显示高电平、低电平、中电平、高阻态、脉冲信号。注意有“高阻态”测试功能。 5、独立的标准时钟频率20个。20M~0.5HZ,从低到高20组时钟可供选择(对于初学者多频可选很重要)。 6、电源有自动保护的+5V,+12V、-12V、、+3.3V、2.5V+、1.2V。 7、8个LED放光二级管,8个拨码开关,扬声器。 8、DDS信号输出口及幅度、偏移调谐。 9、6个标准可扩展IO十芯座,1个十四芯座;4组可扩展模块座,1个可扩展DDS模块座、一个可扩展7寸彩屏液晶座; 10、CPLD3032 11、含扫描的智能译码电路模块,12个按键、其中按键可切换成脉冲式、高低电平式、输出4位二进制式电路模式,8数码可切换成直通非译码动态扫描式、智能BCD译码、16进制译码;16个发光二极管; 第三部分:扩展模块(基本配置,用户根据实际需要,可自行选择,也可自己设计定做) 以下模块供用户自行选择

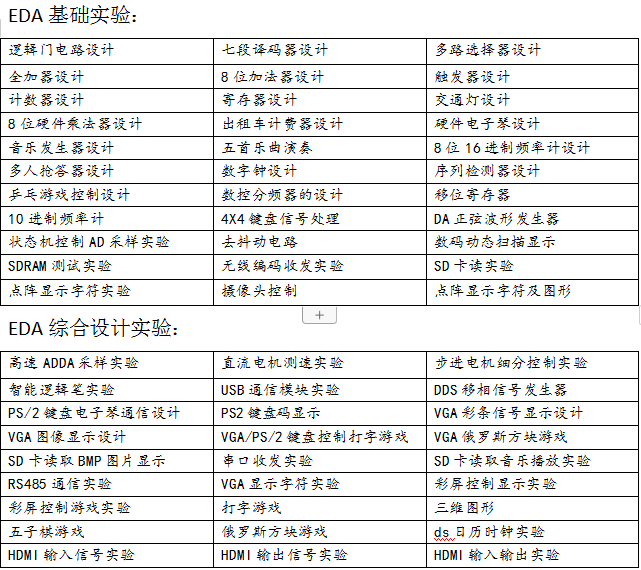

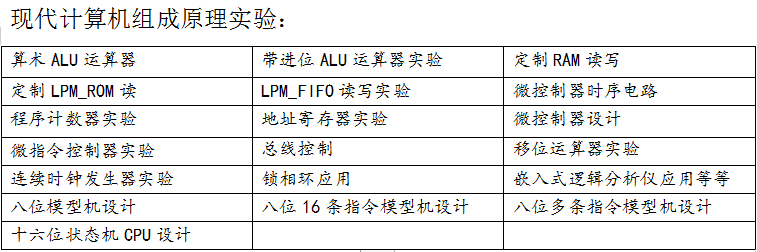

扩展后提供实验(根据硬件配置完成以下实验)

|