|

现代计算机组成原理

收藏

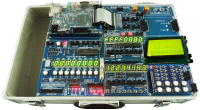

FPGA综合实验箱-现代计算机组成原理 一、特色: ▲单片完成CPU设计 ✦基于FPGA单片完成模型机及部件设计。 ✦功能强大的EDA软件可实时探测每个点的数据信息。 ▲模块化结构 ✦实验箱采用模块化结构:核心板、基础实验、拓展模块三部分,无需手工连线,实验操作简便。 ✦玻璃防尘罩防护。 ▲预留升级通道 ✦接口采用标准化结构,核心板等模块可更换、可升级,资源利用充分,节约。 ▲配备动态配置IO-可重构实验电路结构 ✦智能切换实验电路模式,让有限的IO“流动”起来,不局限于同一“岗位”。 ✦由浅入深、递进式教学,增量实验数目,涵盖实验项目,极力满足基础实验需求。 ▲拓展模块自选、定制或自制 ✦扩展模块根据教学要求自选或定制,亦可自制,有需要配,不需要删,物尽其用,不浪费。 详细参数配置、资料请联系售前:QQ、电话:0571-8891457、 手机:18167105296 一、提供实验(除实现基础和硬件配备实验外,有些需要外设模块) (1)、计算机组成原理实验(基于FPGA单片完成) 1、八位算术逻辑运算ALU 2、八位带进位位算术逻辑运算ALU 3、移位寄存器 4、LPM_ROM读取实验 5、LPM_RAM读写实验 6、FIFO实验 7、总线控制实验 8、节拍发生器系列实验 9、程序计数器PC与地址寄存器AR 10、指令控制电路等实验 11、8位模型机实验 12、含16条指令的CPU设计与实现 13、较复杂CPU应用程序设计实验 14、16位ALU 15、16位比较器COMP 16、16位基本寄存器 17、寄存器阵列 18、16位移位寄存器 19、16位数据寄存器 20、16位单步节拍发生器 21、16位比较强COMP 22、16位基本寄存器 23、16位寄存器阵列 24、16位完整CPU模型机 25、32位RISC-V CPU实验 (2)、数字电路基础实验:(可完成组合逻辑,时序逻辑电路实验配套《数字电子技术基础》教材) 1、数字逻辑电路及74系列实验。 1、脉冲发生器 2、8位比较器 3、8位串行进位加法器 4、16进制七段译码器 5、5人表决器 6、反馈清零法构建12进制加法计数器 7、反馈置数法构建12进制加法计数器 8、8位二进制可预置计数器 9、10位加法计数器 10、D触发器的机械键去抖动电路设计 11、8通道延时电路设计(延时800ns) 12、用74系列宏模块设计两种不同类型的计数器 13、基于LPM的16位可逆计数器设计 14、基于一般模型的计数器设计 15、键触点消抖动电路设计 16、序列发生器设计 17、洗衣机控制电路设计 18、电梯控制电路设计 19、自动售货机控制电路 20、查找表硬件运算器设计 (3)、EDA基础及综合设计实验 1、四位二进制计数器 2、多路选择器 3、逻辑门电路实验 4、触发器实验 5、8位HDL加法器实验 6、7段译码器设计 7、数控分频器 8、8位原理图加法器实验 9、移位寄存器实验 10、序列检测器 11、16进制频率计 12、10进制频率计设计 13、交通灯实验 14、抢答器 15、出租车计费器 16、数字钟 17、硬件电子琴 18、梁祝演奏电路 19、5首音乐演奏电路 20、乒乓球游戏 21、8位乘法器实验 22、8位动态扫描实验 23、动态扫描数码管秒表实验 24、按键去抖动电路 27、倒计时交通灯设计 28、小流水灯实验 29、4X4键盘显示 30、16X16小点阵实验 31、PS2_piano电子琴 32、VGA显示图像 33、VGA三维显示 34、USB转串口通信实验 二、提供资料 1、提供实验部分所以源码 2、提供实验平台的说明手册和实验手册、实验PPT等、实验操作视频。 3、配套教材清华大学教材:《EDA技术与Verilog HDL》第六版,《数字电路技术基础》第三版,《现代计算机组成原理》第二版(可自行订购) 4、提供扩展板原理图 5、提供配套软件QuartusII18.1及配套软件 6、提供芯片技术手册 三、实验箱总体要求: 1、采用实验箱结构; 2、实验电路板装载在实验箱; 四、实验台技术性能: 1、输入电源:单相三线220V±10% 50Hz 2、工作环境:温度-10℃~+40℃ 相对湿度<85%(25℃) 3、外形尺寸: 49X23.5X13CM、装置容量:<20W 4、箱体采用铝合金包边,防火面板。 5、输入电源:22V±10% 50Hz; 6、系统有保护电路,稳定可靠、可扩展; 7、提供丰富详实的计算机组成原理基础实验、EDA基础实验、综合开发实验、数字电路实验,及配套最新软件资源。 五、核心板硬件接口要求: (一)、系统分四大部分 核心板+动态配置IO模块+扩展部分)(模块配带玻璃防尘罩,可对电子元件防灰尘防触摸,提高使用寿命) (1)、核心板(Intel) 1、板载USB-Blaster集成下载器 2、USB转串口 3、串行存储器64Mbit 4、掉电配置器件EPCS16 5、50M时钟源 6、4组LED 7、4组动按键 8、FPGA Cyclone 10 10CL006F256,BGA封装256脚 9、4组 40芯144个IO脚扩展座 10、TF座 (2)、动态配置IO-可重构实验电路结构模块 1、提供不少于11套实验电路模式,不少于64组IO脚可动态配置,可同时输入输出各32位二进制数据(适合计算机类课程学习); 2、64组IO在不同实验模式下,IO锁定的位置不同。 3、8数码管可切换成带有自动译码器式,七段译码式、动态扫描式等电路。 4、提供12组LED可切换成并行式、串行式、4位一组累加式。 5、其中8组按键可切换成高、低电平式、单脉冲式、琴键式、消抖动和非消抖动式、单键一次输入四位式,8组能同时输入32位二进制式。 6、时钟选择0.5Hz-50MHz,共20组,可通过1个按键进行选择,一个按键进行对系统复位。 7、提供1.77寸LCD,可对电路模式进行显示、显示输入16进制输入信号,可同时可显示32位,可显示当前选择的频率值。 8、配备2组PS/2、蜂鸣器、温度传感器。 9、USB接口,可独立对此板供电,并备有串口通信功能。 (3)、扩展基板: 1、提供铝制及防火板材料箱体。 2、提供220V电源输入,并进开关电源输出5V,电流不低于3A。 3、6组可接插扩展板标准 40 芯座,共144 个 I/O 扩展到 6 个扩展座上。 (4)、扩展模块(无需排线,可螺丝固定,可更换) 1、16组LED+16组拨码开关模块 2、36组LED模块 3、36组拨码开关 4、128*64点阵显示屏,可显示模型机的运行数据。 5、SD+2组PS/2+CPLD3032+VGA模块 6、4X4矩阵键盘模块 |